# Compact Low-Power mm-wave ICs for Next-Generation (5G/6G) Wireless Transceivers

Domenico Zito

AGH University of Science and Technology, Krakow, Poland domenico.zito@icloud.com

#### **Outline**

- Ultra-Scaled Silicon Technologies

- Impact of passive losses in low-power mm-wave ICs

- Low-Power Compact mm-wave ICs for 5G/6G

Phased-Array Transceivers

- Variable-Gain Low Noise Amplifier

- Benchmarking and validation (rvt vs. slvt)

- Conclusions

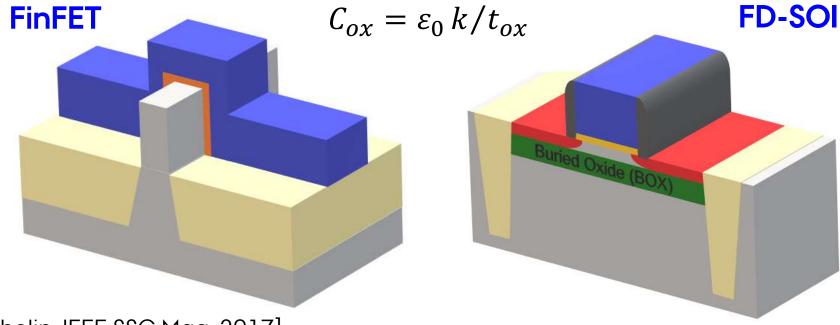

#### Si Tech Evo: CMOS Techs

- Ultra-scaled device evolution driven by charge control improvement and leakage current reduction

- Two fully depleted (FD) techs emerged with 22/28nm

CMOS node (double patterned, high-k dielectrics, metal gate, strained Silicon)

[Cathelin, IEEE SSC Mag. 2017]

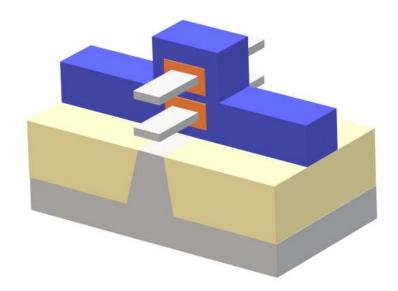

#### Si Tech Evo: The "Last" CMOS Transistors

- Samsung has introduced a different transistor design starting from the 3nm node

- The next transistor has already many names

- gate-all-around

- multi-bridge channel

- nano-beam

- nano-sheet

[Ye, Ernst, Khare, IEEE Spectrum, Jul. 2019]

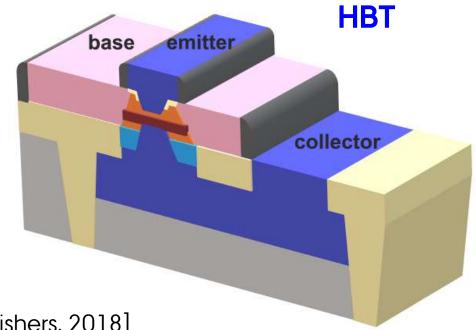

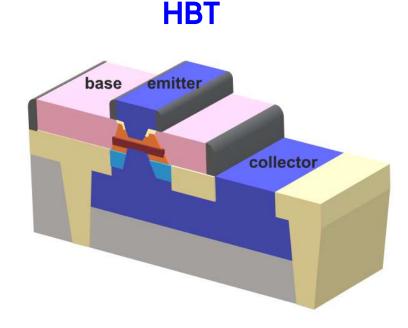

#### Si Tech Evo: SiGe BiCMOS Techs

- Device evolution driven by **higher frequency operations**  $(f_{T_i} f_{max})$  and **integration with scaled CMOS devices**

- High-speed SiGe/SiGe:C Heterojunction Bipolar Transistors (HBTs) together with high-density CMOS

•

$$f_{max} \approx \sqrt{\frac{f_T}{8\pi R_B C_{BC}}}$$

R<sub>B</sub>: base resistance

C<sub>BC</sub>: base-collector capacitance

[Rücker, Heinemann, Ch. 1, River Publishers, 2018]

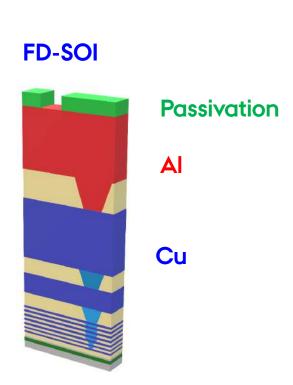

#### Si Tech Evo: SiGe BiCMOS Advantages

- **HBT** f<sub>T</sub> less sensitive to parasitic capacitance of metal layers

- More mature back-end-of-line (BEOL), leading to better passives

- Lower costs

[Chevalier et al. IEEE BCICTS 2018]

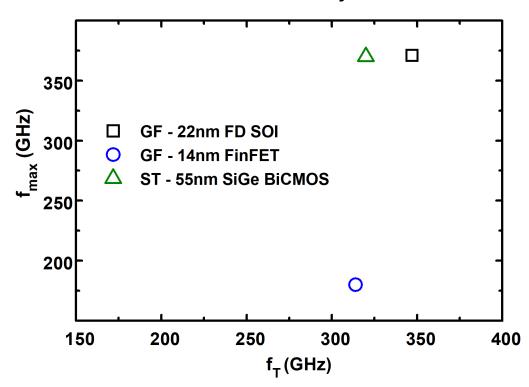

#### Si Tech Evo: FoMs

• FinFET, FD-SOI and HBT devices commercially available

$$-f_T > 300 \text{ GHz}$$

$-f_{max} > 150 \text{ GHz}$

Active devices have outstanding performances with great potential for high-frequency applications

[Ong et al. IEEE RFIC 2018] [Chevalier et al. IEEE IEDM 2014]

#### Si Tech Evo: mm-wave Applications

- These outstanding performances are enabling a plethora of applications

- High data-rate communications for next generation wireless networks (5G and beyond)

- High-speed wireline communications

- Autonomous and near-autonomous vehicles

- Virtual reality

- Radio astronomy

- Earth observations

- Satellite communications

- Quantum computing

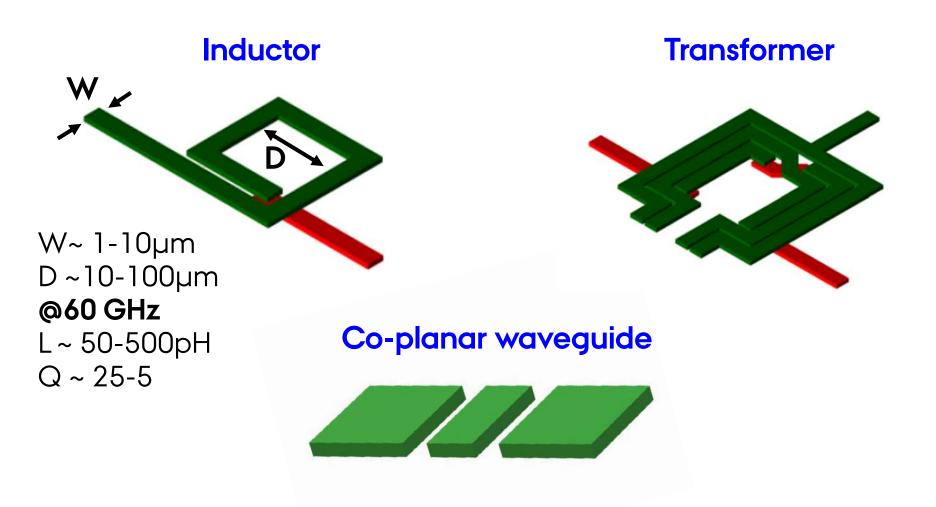

#### Si Tech Evo: Inductors, Transformers, TX Lines

[Pepe, et al. ISSC 2016]

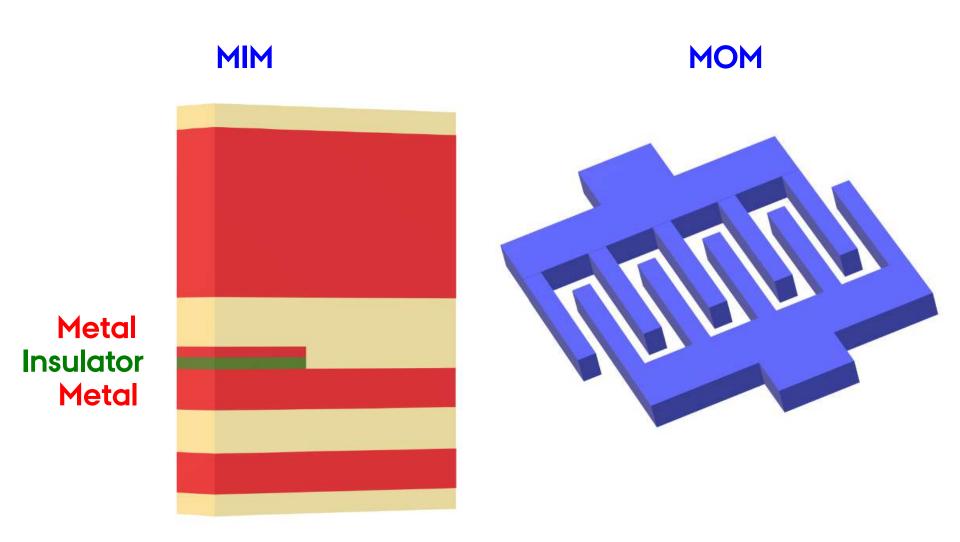

## Si Tech Evo: Capacitors

## Si Tech Evo: Back-End-Of-Line (BEOL)

The impact of losses in passives

**BiCMOS**

Losses have a dramatic impact on performance ⇒ up to 100%

# Impact of Losses: Traditional Loss-Less Design Methodology

#### AN maximum stable gain

## 25 S<sup>SN</sup> 24 23 55 56 57 58 59 60 61 62 63 64 65 f(GHz)

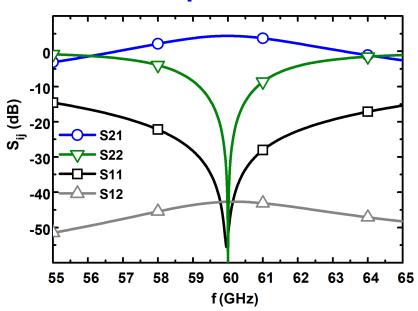

#### **LNA S-parameters**

- Despite AN maximum stable gain  $(G_{MSG}^{AN})$  of **24.4 dB**, MN losses reduce  $S_{21}$  to **4.4 dB**!

- Losses spoil transistor gain potential

# Impact of losses: advanced loss-aware design methodology

#### AN maximum stable gain

## 25 SSE 24 23 55 56 57 58 59 60 61 62 63 64 65 f(GHz)

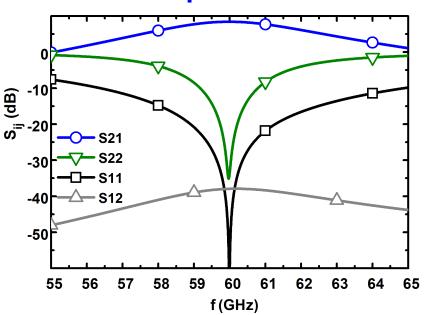

#### **LNA S-parameters**

- Despite AN maximum stable gain  $(G_{MSG}^{AN})$  of **23.2 dB**, MN losses reduce  $S_{21}$  to **8.4 dB**

- The loss-aware methodology reduces the impact of losses

## Takeaways (1/2)

- The evolution of silicon technologies has led to transistors with excellent performance for operation at mm-waves

- However, losses in passive devices impede the full exploitation of transistors potential for low-power mm-wave ICs

- Our case study on mm-wave LNA design unveils (quantitatively) the dramatic performance degradation due to MN losses and the benefits of loss-aware design strategies

[Zito et al. IEEE ISC 2019]

## Takeaways (2/2)

- The results indicate the strong need of further technology advances towards better passives

- new materials

- new technology processes

- Also, loss-aware design methodologies are a must and key to design ICs and systems in the mm-wave frequency range and beyond - especially for low-power ICs

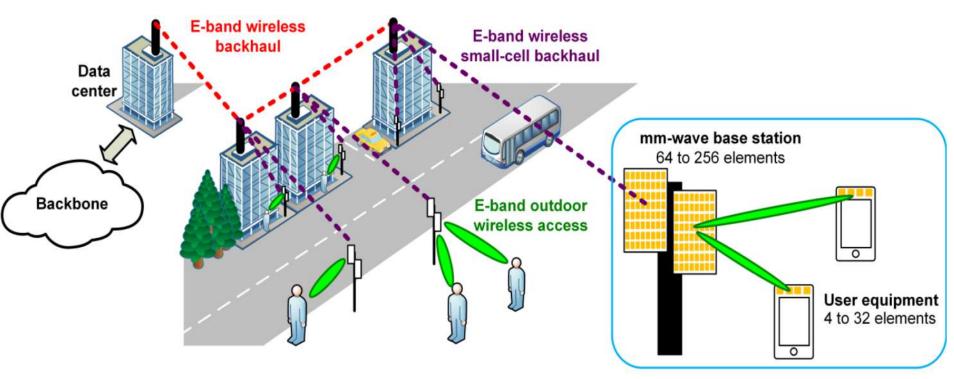

- E-Band point-to-point & point-to-multi-point Wireless Local Area Networks & Broadband Internet Access

- Massive MIMO Systems

- Data Centers (Clouds)

- 60 GHz Uncompressed Wireless HD Video Area Networks

- -2.5 Gb/s

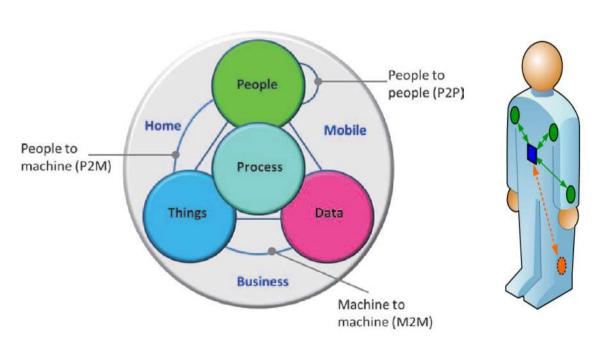

- Internet of Things (IoT) Internet of Everything!

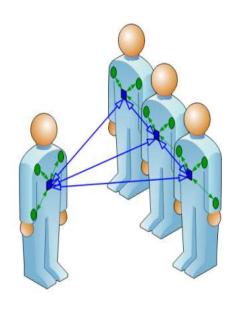

- P2P, P2M and M2M communications & contactless sensing

- 60 GHz On- & Off-body communications

E-Walls, e-Cars (autonomous/driverless vehicles)

(Source: IEEE Spectrum)

(Source: IEEE Spectrum)

- Complex (Cyber-Physical) Autonomous Systems

- Autonomous and near-autonomous vehicles

- Collision-avoidance automotive radars

- Vehicle-to-Vehicle and Vehicle-to-All Communications

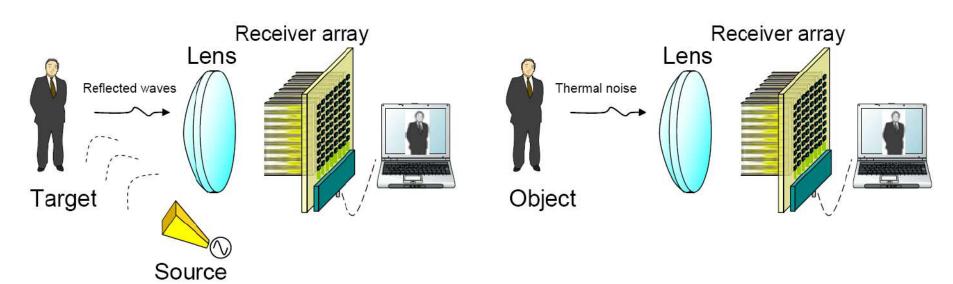

Active & Passive Imagers

(a) Active imaging sensor (b) Passive imaging sensor

[Mereni et al. AICSP. Springer, 2013]

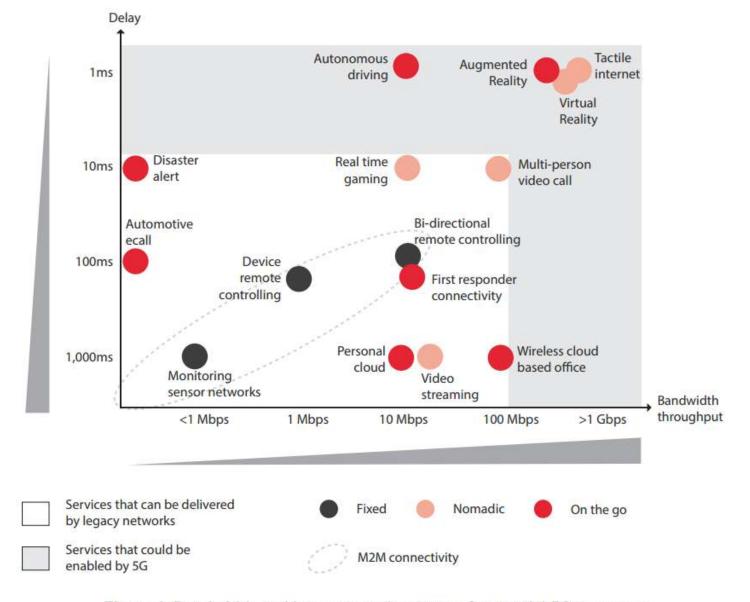

- Expected by 2020

- Massive growth in data traffic volume (×1000)

- Massive growth in connected devices (25 Billion devices)

- Key drivers for the development of 5G

- Low latency (< 1ms)

- High throughput (>1Gb/s)

[Rappaport et al. IEEE Access 2013] [Koverman. IEEE Consumer Elec. Mag. 2016]

22

## Next-Generation (5G) Wireless Comms

• 3D (Data-rate, Delay, Devices) **Data Capacity Devices** (data highways) Responsive Objects ("real time") Bandwidth -> mm-wave Delay **Transceivers** Gb/s Data-rate

Figure 1: Bandwidth and latency requirements of potential 5G use cases

Source: GSMA Intelligence

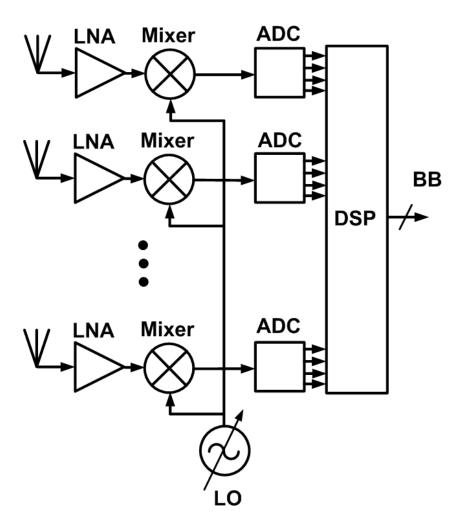

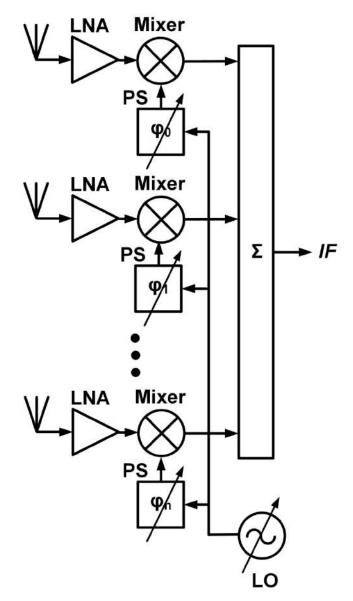

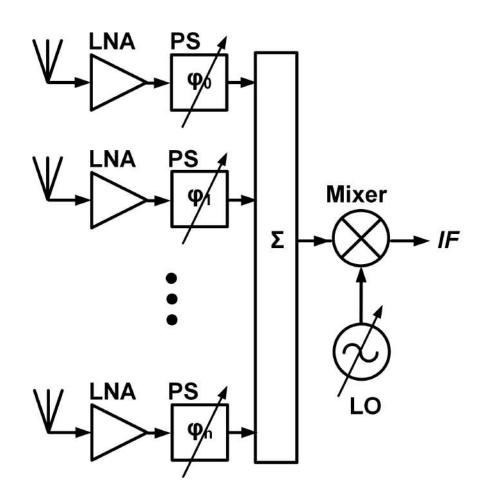

- Phased-Array Architectures

- Digital (BB) phase shifting

- True MIMO

- Phased-Array Architectures

- IF phase shifting

- "Pseudo" MIMO (MISO)

- Phased-Array Architectures

- LO phase shifting

- "Pseudo" MIMO (MISO)

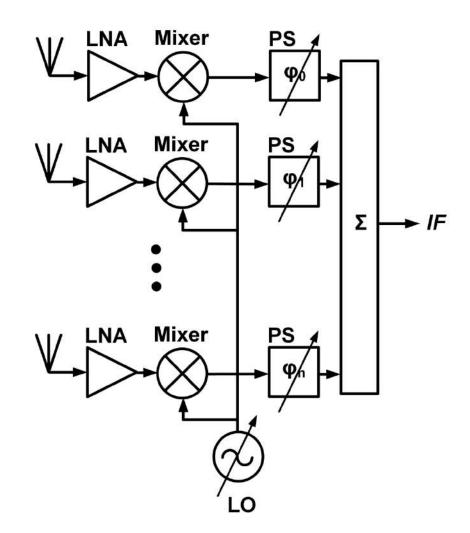

- Phased-Array Architectures

- RF phase shifting

- "Pseudo" MIMO (MISO)

- 60 GHz Uncompressed Wireless HD Video Area Network

- Commercial development (SiBeam)

Source Transceiver (32 TX / 4 RX)

Sink Transceiver (32 RX / 8 TX)

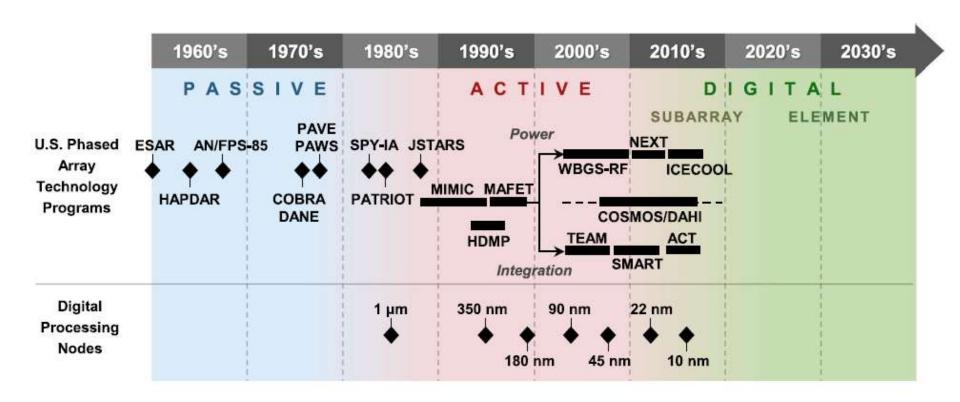

Evolution timeline

Fig. 1. U.S. phased array technology development programs and digital processing nodes timeline.

[Herd et al. Proc. of the IEEE 2016]

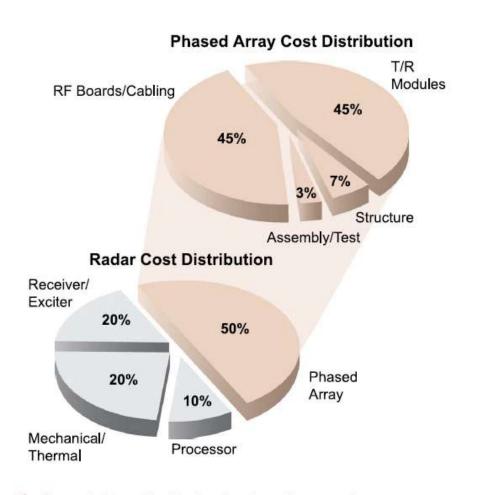

- Cost distribution

- Phased-array: 50%

Fig. 9. Typical cost distribution for phased array radar.

[Herd at al. Proc. of the IEEE 2016]

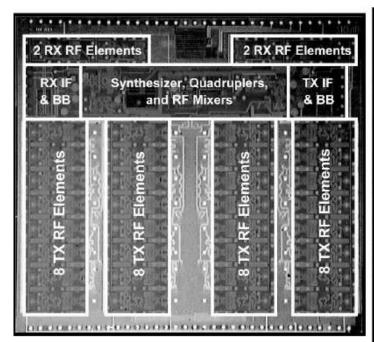

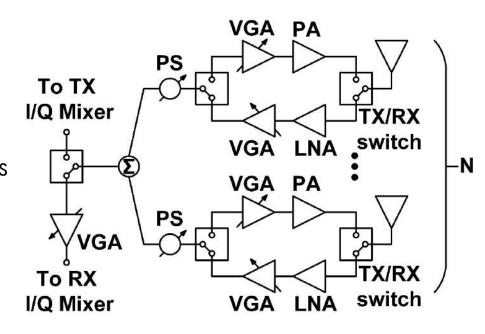

#### 5G/6G Phased-Array Transceivers ICs

- 5G New Radio (NR) standard

- Freq. Range 2 (FR2): 24.25-52.6 GHz

- Fosters research on phased-array ICs

- First-reported 28GHz IC for 5G

- 32 TX/RX (TRX) elements

- LNA with 12dB gain & 6dB NF (incl. TRX switch losses)

- Phase-invariant VGA ⇒ beam shaping

[Sadhu, IEEE JSSC, 2017]

[Spasaro and Zito. IEEE IMS 2022]

### **VG-LNAs for Phased-Array ICs**

- ICs with RF phase shifting

- VG-LNA ⇒ no VGA ⇒ power/area saving

- Switchless TRX architectures relax

gain & NF requirements for LNAs

⇒ Enable low-power designs

- To TX

I/Q Mixer

PS VGA PA

PS VGA PA

PS VGA LNA

TO RX

I/Q Mixer

VGA

PS VGA LNA

PS VGA LNA

- ICs with digital beamforming [Gao, IEEE T-MTT, 2021]

- Compact low-power VG-LNAs are key for 5G/6G RXs

- Complexity reduction, performance enhancement and functionality extension

- Cost-effective (small form factor) and energy-efficient (low power) solutions

#### Sub-mW 30 GHz VG-LNA

- Prior-art VG-LNAs operating in 5G NR FR2

- Power consumption: a few/tens of milliwatts

- Silicon area larger than 0.1 mm<sup>2</sup>

- Sub-mW 30GHz VG-LNA in 22nm FDSOI CMOS

- Core area: 0.044 mm<sup>2</sup>

- Designed for low-power tapered phased array

- Taylor window taper up to 18 dB

- Planar 8x8 antenna array

[Spasaro and Zito. IEEE IMS 2022]

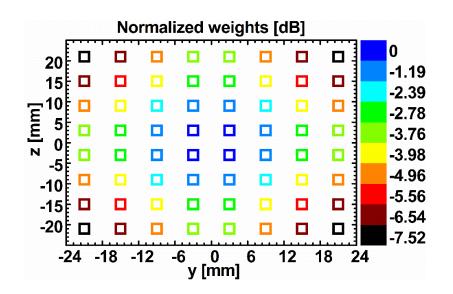

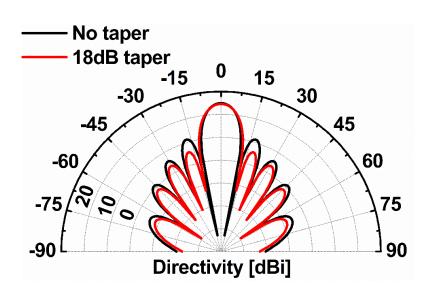

#### Requirements for Gain Control: Tapering

Normalized weights

Radiation pattern of antenna array

- 30GHz 8×8 3GPP TR 38.901 compliant-antenna array (6mm pitch)

- 18dB Taylor window taper ⇒ 7.5dB gain-control range required

## Requirements for Gain Control: VG-LNA

- VG-LNA design goals

- 8dB gain control range

- sub-mW P<sub>C</sub> for all gain states

- Peak gain of 16 dB for high-gain state

- 6dB NF, similarly to other designs [Sadhu, IEEE JSSC, 2017]

- In absence of blockers, max. sensitivity condition: Uniform weigths

& high gain ⇒ SNR after beamforming network improves by

10×Log<sub>10</sub>(64) = 18 dB

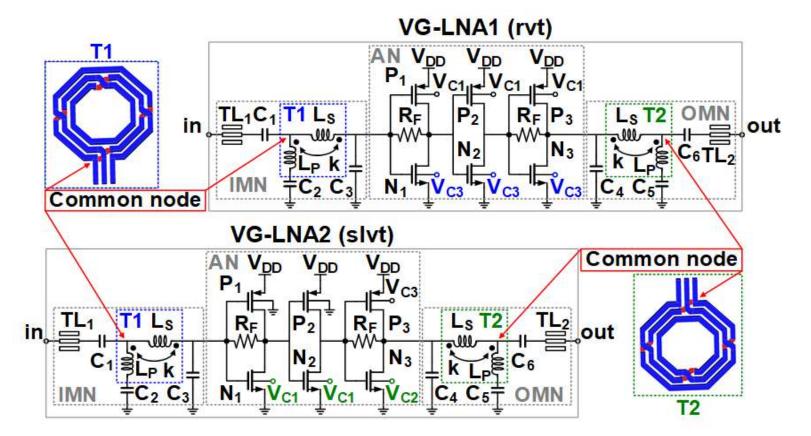

### **VG-LNA Features: Circuit**

- Inductorless active network (AN)

- Feedworward input (IMN) & output (OMN) matching networks

- Nominal gain of 12 dB with P<sub>C</sub> of 0.6 mW

- Single gain-control voltage  $V_{CN} = V_C$  (with  $V_{CP} = 0 \text{ V}$ )

## **VG-LNA Features: Low-Power Techniques**

- Inductorless AN with current reuse and three gain stages

- No peaking inductors or inter-stage matching networks (MNs)

- Compact layout

- Reduced parasitics/lossy interconnects

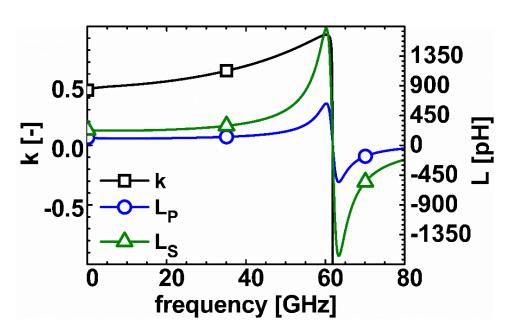

- MNs with cascaded L-network stages and coupled inductors

- Compact layout

- Coupling factor (k) & intermediate impedance as free parameters

- Enable integration and NF optimization

[Spasaro et al. IEEE IMS 2022] [Spasaro et al. IEEE TCAS-II 2023]

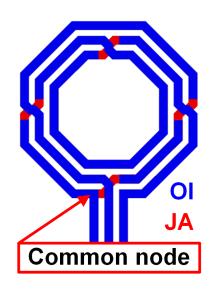

#### **VG-LNA Features: Transformer**

- Top-most copper metal layers (JA and OI)

- $L_P = 119 \text{ pH}$ ,  $L_S = 267 \text{ pH}$ , and k = 0.59 at 30 GHz

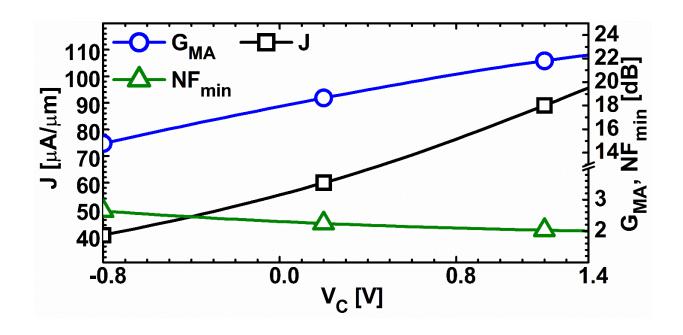

#### **VG-LNA Features: Gain Control**

- Post-layout simulations (PLS)

- Transistor current density (J)

- Max. available gain  $(G_{MA})$  and  $NF_{min}$  of AN at 30 GHz

- $G_{MA}$  increases from 15 dB to 22 dB as control voltage ( $V_C$ ) increases

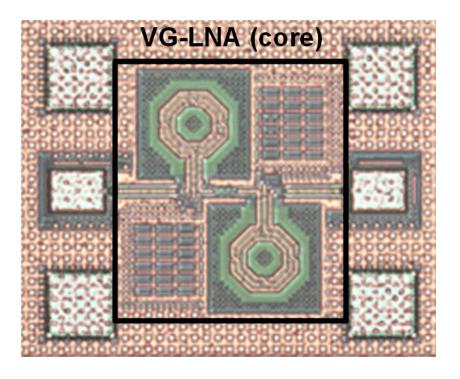

## VG-LNA Meas. Results: Test Chip

- Silicon area

- Core: 0.20×0.22 mm<sup>2</sup>

- With pads:  $0.32\times0.26$  mm<sup>2</sup>

- On-die measurements

- PNA-X N5245A

- Power meter N1914A

- Power sensor N8487A

- ECal N4693A

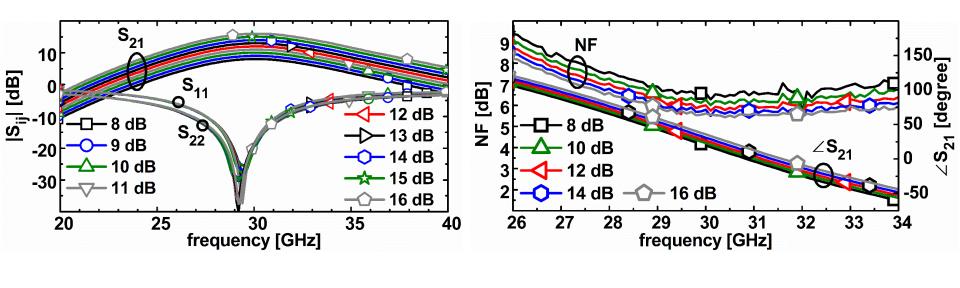

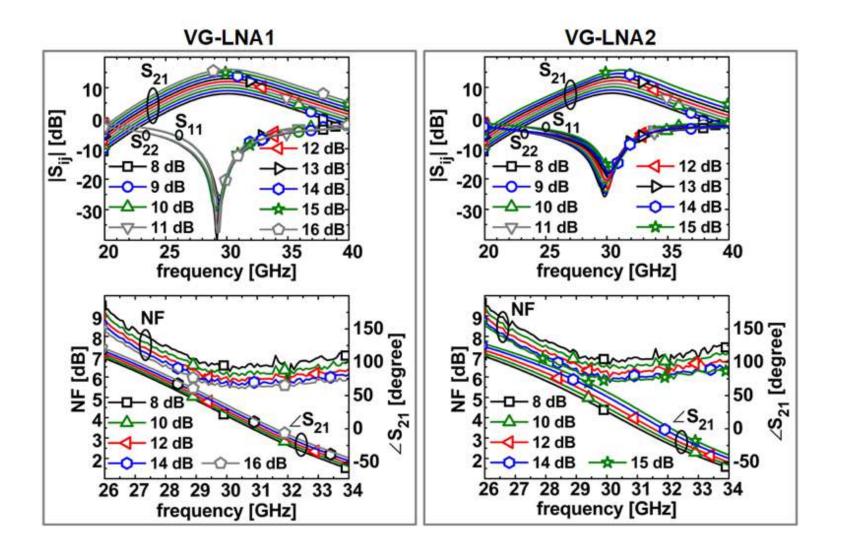

#### VG-LNA Meas. Results: S-Parameters & NF

- High gain:  $S_{21} = 16$  dB at 30.1 GHz, NF = 5.5 dB,  $P_C = 0.97$  mW

- Low gain:  $S_{21}$  = 8 dB at 30.1 GHz, NF = 6.3 dB,  $P_C$  = 0.41 mW

- Variation of  $\angle S_{21}$  in the 7GHz BW<sub>3dB</sub>:  $\Delta \varphi_{21} < 16.7^{\circ}$

S-parameters

$\angle S_{21}$  and NF

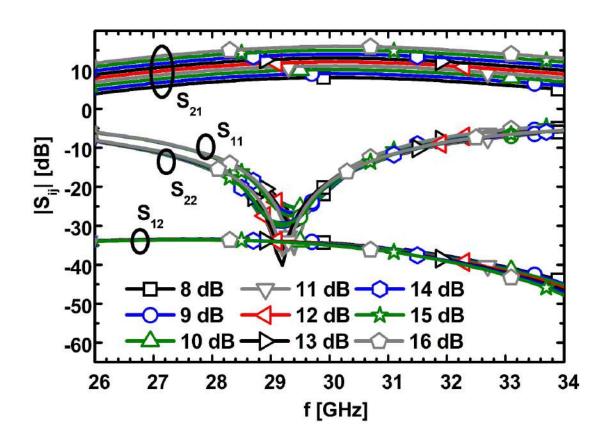

#### **VG-LNA Meas. S-Parameters**

Isolation > 30 dB (important result)

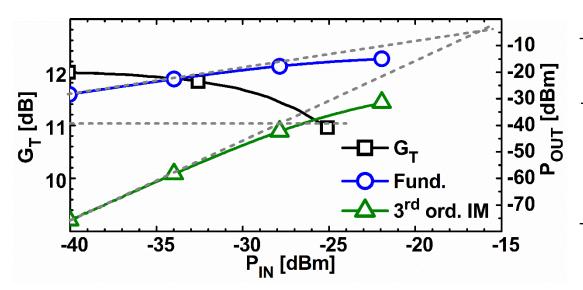

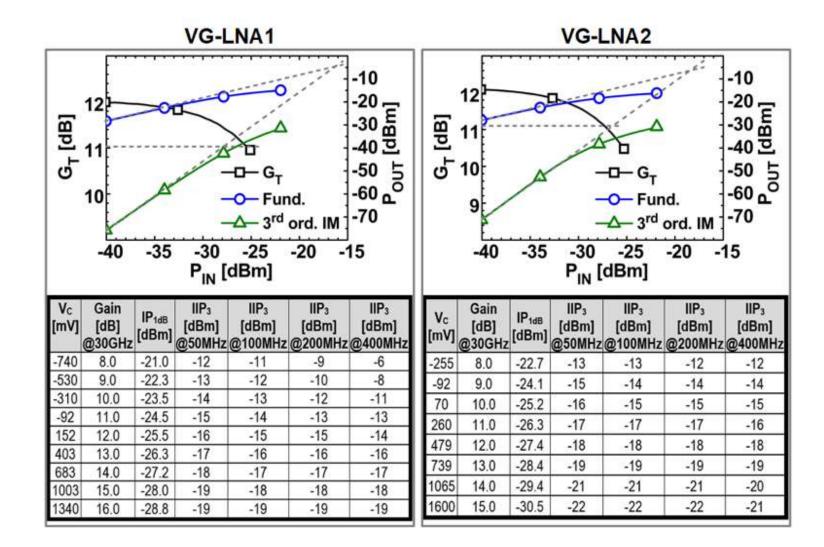

## **VG-LNA Meas. Results: Linearity**

| Gain [dB] | IP <sub>1dB</sub><br>[dBm] | IIP <sub>3</sub> [dBm] |  |  |  |  |

|-----------|----------------------------|------------------------|--|--|--|--|

| 16        | -28.8                      | -19                    |  |  |  |  |

| 12        | -25.5                      | -16                    |  |  |  |  |

| 8         | -21.0                      | -12                    |  |  |  |  |

Nominal (12dB gain)

- Transducer gain ( $G_T$ ) at 30 GHz

- IP<sub>3</sub> for input tones at 30 and 30.05 GHz (as per 5G channelization)

# VG-LNA Meas. Results: Comparison with Prior Art

| Ref.                          | Tech.<br>[nm] | S <sub>21</sub><br>[dB] | f <sub>C</sub><br>[GHz] | BW <sub>3dB</sub><br>[GHz] | NF<br>[dB]     | IP <sub>1dB</sub><br>[dBm] | Δφ <sub>21</sub><br>[°] | P <sub>C</sub><br>[mW] | Area<br>[mm²] |

|-------------------------------|---------------|-------------------------|-------------------------|----------------------------|----------------|----------------------------|-------------------------|------------------------|---------------|

| This                          | 22<br>FDSOI   | 16<br>8                 | 30.1<br>30.1            | 7.1<br>7.2                 | >5.5<br>>6.3   | -28.8<br>-21.0             | 16.7                    | 0.97<br>0.41           | 0.044         |

| [T-MTT,<br>2021] <sup>1</sup> | 22<br>FDSOI   | 24.2<br>16.2            | 30.4<br>30.4            | 23.7<br>23.7               | >2.4<br>>3.0   | -25<br>-19                 | -                       | 16<br>16               | -             |

| [MWCL,<br>2018]               | 40<br>Bulk    | 27.1<br>18.4            | 27.1<br>27.8            | 7.4<br>9.3                 | >3.3<br>>3.4   | -21.6<br>-13.4             | 18                      | 31.4<br>21.5           | 0.26          |

| [MWCL, 2019]                  | 65<br>Bulk    | 20.8<br>10.2            | 30.4<br>30.4            | 4<br>4                     | <b>&gt;3.7</b> | -20.4<br>-                 | 8                       | 26.7<br>16.5           | 0.20          |

| [IMS,<br>2021]                | 90<br>Bulk    | 21.4<br>11.6            | 37<br>37                | 11.3<br>11.3               | >4.7<br>-      | -25.1<br>-22               | 7.2                     | 17.9<br>17.9           | 0.452         |

| [IWS,<br>2021]                | 65<br>Bulk    | 11.4<br>-5              | 28<br>28                | 11.5<br>-                  | >4.7<br>-      | -                          | -                       | 2.16<br>-              | 0.13          |

<sup>&</sup>lt;sup>1</sup>Simulation results; <sup>2</sup>including pads

## Benchmarking and Validation: rvt vs. slvt MOSFETs

- Inductorless active network (AN), with IMN & OMN

- 12dB nominal gain with  $P_C = 0.6 \text{ mW}$

- Single gain-control voltage: VG-LNA1 ( $V_{C1}=0$  V,  $V_{C3}=V_{C}$ ); VG-LNA2 ( $V_{C3}=0$  V,  $V_{C1}=V_{C2}=V_{C}$ )

## Benchmarking and Validation: Test Chips

# Benchmarking and Validation: Performance (1/2)

# Benchmarking and Validation: Performances (2/2)

# Benchmarhing and Validation: Comparison with Prior-Art VG-LNAs in 5G NR FR2

| Work                            | VG-L               | NA2            | VG-LNA1 [6]        |                           | [2]1       |       | [3]       |       | [4]       |       | [5]       |       | [19]     |    |

|---------------------------------|--------------------|----------------|--------------------|---------------------------|------------|-------|-----------|-------|-----------|-------|-----------|-------|----------|----|

| CMOS Tech.<br>[nm]              | 22 (FDSOI)         |                | 22 (FDSOI)         |                           | 22 (FDSOI) |       | 40 (Bulk) |       | 65 (Bulk) |       | 90 (Bulk) |       | 65(Bulk) |    |

| Peak gain<br>[dB]               | 15.7               | 8.1            | 16                 | 8.0                       | 24.2       | 16.22 | 27.1      | 18.4  | 20.8      | 10.2  | 21.4      | 11.6  | 11.4     | -5 |

| fc [GHz]                        | 31.2               | 30.4           | 30.1               | 30.1                      | 30.45      | 30.45 | 27.1      | 27.8  | 30.42     | 30.42 | 37        | 372   | 28       | 28 |

| BW <sub>3dB</sub> [GHz]         | 5.7                | 6.4            | 7.1                | 7.2                       | 23.7       | 23.72 | 7.4       | 9.3   | 4         | 42    | 11.34     | 11.32 | 11.5     |    |

| Min. NF [dB]                    | 5.9                | 6.9            | 5.5                | 6.3                       | 2.4        | 3.0   | 3.3       | 3.4   | 3.7       | -     | > 4.7     | -     | > 4.7    |    |

| IP <sub>1dB</sub> [dBm]         | -30.5 <sup>3</sup> | <b>-22</b> .7³ | -28.8 <sup>3</sup> | <b>-21.0</b> <sup>3</sup> | -25        | -19   | -21.6     | -13.4 | -20.4     | -     | -25.15    | -222  | -        | -  |

| ∠S <sub>21</sub> variation* [°] | 29.5               |                | 16.7               |                           | -          |       | 18        |       | 8         |       | 7.2       |       | -        |    |

| Pc [mW]                         | 0.91               | 0.40           | 0.97               | 0.41                      | 16         | 16    | 31.4      | 21.5  | 26.7      | 16.5  | 17.9      | 17.9  | 2.16     | a- |

| Core area [mm²]                 | 0.044              |                | 0.044 0.044        |                           | -          |       | 0.26      |       | 0.20      |       | 0.456     |       | 0.13     |    |

<sup>&</sup>lt;sup>1</sup>Simulation results; <sup>2</sup>deduced from plots; <sup>3</sup>measured at 30 GHz; <sup>4</sup>dual band (26-30.5 GHz and 33.8-40.6 GHz) <sup>5</sup>calculated from available data; <sup>6</sup>including pads; <sup>\*</sup>max variation in 3dB band.

#### **VG-LNA: Conclusions**

- 30GHz VG-LNA with 8dB gain-control range

- Record power consumption (world-1st sub-mW) and area on silicon

- Compliant with targeted tapered phased-array IC with switchless TRXs

- 4-to-32 VG-LNA units consume less than one unit of prior-art VG-LNAs

- Very compact size (one or more orders of magnitude)

- S<sub>21</sub> phase variation, IP<sub>1dB</sub>, BW<sub>3dB</sub>, & NF comparable with prior works

- Benchmarging and validation across technology flavours (rvt and slvt)

- Higher frequency limitations

#### **Conclusions**

- Ultra-scaled Silicon techs show the largest potentional as platform for many current and future emerging technologies (e.g. wireless and quantum), but the losses require innovative topologies and loss-aware design methodologies

- Our ultimate innovative (new design paradigm) building blocks with world-record performance – These have open new technology developments and technology directions (Wireless, IoTs & Quantum) – transistor-size low-power mm-wave ICs

## Acknowledgments

This work has been co-funded by the European Union's Horizon 2020 Research & Innovation Programme through the FET Open project IQubits under Grant Agreement N. 829005

This lecture has been co-funded by IEEE CASS Distinguished Lecturer Programme & IEEE CAS France Chapter

## **Sponsors**